Tanner 應用系列|適合類比 / 混合訊號 IC 設計的全流程解決方案

- Enlight Technology

- Apr 26, 2022

- 11 min read

Siemens EDA IC 全流程

Siemens EDA 全流程有一個豐富的環境,高度可配置且非常靈活,為混合信號設計人員提供了許多易用功能。該流程經過優化,適用於創建 22nm 的定制模擬 IC 或 “類比為頂層” 的混合訊號 IC。它包含高度集成的前端和後端工具,從原理圖輸入到混合訊號模擬和波形檢索、查看及 RTL 網表綜合,再到佈局佈線、物理版圖實現以及晶圓廠認證的 Calibre® 平臺物理驗證。透過集成協力廠商工具支援互通性、多用戶和版本控制的Open Access 資料格式管控。該全流程套件有一個庫管理器,其為管理和流覽所有設計庫、單元和視圖提供一個統一的介面,並且提供對 IC Manage、Cliosoft 和 SubVersion (SVN) 版本控制軟體的支援。

工藝設計套件 (PDK) 是模擬和定制設計環境的一個重要組成部分,包括 OA 資料、CDF、回檔、網表程式和參數化單元 (PCell)。Siemens EDA 工藝包可以由協力廠商PDK轉換而來,包括回檔和 PCell 代碼。可擴展的自動化質檢流程可以確保Siemens EDA 全流程實現完全一致且完全相容的結果。在Siemens EDA全流程環境中使用的 PDK 獲得廣泛的支援。Siemens EDA 與主要晶圓代工廠建立了強大的工作關係,使得 PDK 可以快速支援其他製程節點。

圖 1:Siemens EDA 全流程。

利用 S-Edit 進行原理圖輸入

S-Edit

S-Edit 是一個全功能原理圖輸入環境,通過一個直觀且高度可定制的圖形介面與所有西門子模擬器產品無縫集成。它非常容易使用,可快速上手,只需極少的使用者配置工作,基本上消除了切換工具時常常需要的大量學習時間。利用全面且可自訂的工具列可以輕鬆訪問許多設計功能的快捷方式,提高生產效率,因為無需在複雜的子功能表和下拉選項中查找功能。與設計相關聯的庫和單元、命令視窗以及屬性功能表在 S-Edit 中的位置都很靈活,並且可以分離,易於重新配置以適合任何工作方式或分屏顯示。

圖 2:S-Edit 原理圖輸入環境。

S-Edit 擁有先進的陣列和匯流排支援,易於實現且完全相容的繼承連接,以及可配置的原理圖電氣規則檢查 (ERC)。設計人員可以編輯原理圖和 ERC,然後匯出網表並進行模擬,而無需保存設計。

多種視圖

S-Edit 支援原理圖、SPICE、Verilog、Verilog-A/Verilog-AMS 和 VHDL 視圖,設計人員可以在整個層次結構中逐單元或逐實例地輕鬆切換抽象描述或詳細模型。

原理圖比較

設計人員常常使用現有晶片設計來創建一個新的版本,在這種情況下,設計人員需要將原始 “標準” 電路圖與當前更新的版本進行比較,或者他們可能發現模擬結果與先前的運行不同,因而需要檢查二者的差異。S-Edit 現在擁有非常有用且相當獨特的比較功能,可以比較兩個電路圖或符號視圖以確定更改了什麼內容。所有差異都總結在一個可分離的專用視窗中,針對每個差異可以自動放大並高亮顯示在原理圖中。

圖 3:原理圖比較。

可定制環境

S-Edit 環境可以通過使用者定義功能和功能表來輕鬆定制,環境設置和快速鍵可以使用 Tcl 腳本或下圖所示的內置自訂選單來定制。

圖 4:定制選單。

利用 AFS 和 EZwave 進行模擬

AFS

Analog FastSPICE™ (AFS) 平臺是世界上最快的電路驗證平臺,適用於類比、RF、混合訊號和定制數位電路,並且與 S-Edit 原理圖編輯器完全集成。在 S-Edit 內置的AFS模擬設置介面中,設計人員可以設置和啟動模擬,並在 EZwave™ 軟體波形檢視器中查看結果。在模擬設置功能表中進行的所有更改都存儲在單獨的模擬驗證平臺中,其中包含相關的原理圖,以便簡化設計開始時的驗證。使用者只需打開一個電路圖單元就能訪問、審查或重新運行所有存儲的模擬設置。

圖 5:下拉到 AFS 設置模擬圖形介面。

模擬結果

在 S-Edit 模擬設置對話方塊中,設計人員可以使用 Results (結果) 窗格的 Signals (信號) 部分中的工具列圖示,輕鬆選擇要保存或要在 EZwave 中繪圖的走線電壓和節點電流。直流工作點電壓、電流和交流小信號參數可以直接反向標注到電路圖中。以下是運算放大器的 PSRR 性能的波形示例。

圖 6:EZWave 波形檢視器。

EZwave 計算器集成

S-Edit 模擬設置圖形介面中有一個結果窗格,其與 EZwave 計算器無縫集成,可用於在設計期間構建任何高級運算式和輸出測量。輸出測量結果和高級計算器運算式存儲在 S-Edit 驗證平臺中。模擬完成後,EZwave 繪製結果窗格中的運算式所代表的波形。同一窗格中還會評估和顯示標量結果,如相位裕度或直流環路增益。設計人員可以將運算式發送到計算器 (或從計算器獲取運算式) 以進行進一步編輯,或者在結果窗格中手動修改運算式。

圖 7:設置模擬結果窗格中的計算器。

Tanner Designer

Tanner™ Designer 軟體是一款類比驗證管理工具,可以在方便的資料表格上跟蹤模擬結果,允許團隊快速查看哪些模組符合或不符合規範要求,以及監控驗證進度。整個前端流程 (S-Edit、AFS、EZwave 和 Tanner Designer) 中的工具間具有很強的交互功能,使得模擬設計、驗證和調試的效率更高。

圖 8:Tanner Designer圖形介面。

進行混合訊號驗證

Symphony

類比設計人員被要求在混合訊號設計中實現越來越多的數位內容,例如具有數位控制邏輯的高速 ADC,這是一個挑戰。這些設計需要以非常高的精度和快速執行時間對大型混合訊號網表進行全晶片驗證。Symphony 混合訊號模擬器已集成在 S-Edit 中,並且結合了經過晶圓代工廠認證的領先 AFS 電路模擬器。Questa™ 數字模擬器可對複雜的奈米級混合訊號 IC 進行快速精確的驗證。Symphony 混合訊號模擬器可以對數位和類比設計環境進行模擬,利用簡化的直觀方法來整合這兩種環境。

Symphony 已在廣泛的 IC 和 IC 子系統 (包括 ADC、收發器、電源管理晶片、高頻 PLL/DLL 和感測器) 上得到驗證。Symphony 與 AFS 的有效集成使得 AFS 的性能、容量和準確性得到充分利用。就整個系統而言,Symphony 的準確性和性能也支援運行混合訊號模擬以對電晶體級的模組執行關鍵路徑檢查。

Symphony 易於設置和使用。在 S-Edit 中,設計人員點一下滑鼠就能選擇模擬中某個實例使用何種視圖來描述。支持的視圖包括原理圖、Verilog-A、Verilog、VHDL 和 SPICE。對於初始頂層模擬,設計人員可能希望使用不同的視圖。例如,Verilog-RTL 適用於數位模組,Verilog-A 適用於類比模組,電晶體級視圖或包含寄生參數的 Calibre 網表視圖可提供更高的精度。

圖 9:S-Edit 單元視圖選擇功能表。

邊界元件

對於混合訊號模擬,當跨越域邊界時,設計人員需要告訴模擬器如何連接類比和數位信號。Symphony 使用一種稱為邊界元件 (BE) 的新方法來處理類比-數位邊界跨越情況。在其他工具中,設計人員需使用 Verilog AMS 代碼定義連接模組,非常繁瑣且易於出錯。邊界元件與連接模組的作用相同,但更強大且更易於使用。

在子電路 / 模組內部,連接一般是在相同類型的埠 / 走線之間進行。但是,當連接不同域中的子電路 / 模組時,可能會產生連接的各種組合。這些不同的連接組合產生不同類型的邊界元件,例如“邏輯 (數位) 到電氣 (類比)”,反之亦然;當信號跨越域邊界時,Symphony 會自動添加邊界元件。

圖 10:邊界元件。

在混合訊號設計中,錯誤最常發生在類比模組和數位模組的介面上。介面中的錯誤常常只能在更高層次上確認,例如在 I/O 管腳上 (圖 5)。在 Symphony 中,設計人員可以顯示和分析類比和數位結果,從而説明進行混合訊號調試。

圖 11:混合訊號波形。

利用 L-Edit IC 定製版圖

L-Edit IC

L-Edit IC 是西門子的物理版圖工具,可以通過一些高級編輯和便利性功能加速定製版圖開發。L-Edit IC 基於 OpenAccess 並支持 PCell,非常適合為類比和混合訊號設計構建靈活的版圖模組。PCell 是為基本單元器件而創建並在晶圓代工廠 PDK 中發佈,但也可以為邏輯門構建。L-Edit IC 的環境、選單和快速鍵也是可自訂的。

原理圖驅動的版圖

L-Edit 支援原理圖驅動的版圖 (SDL),因而版圖設計人員可以使用 PCell 和連接資料庫從原理圖創建版圖以節省時間,並確保版圖“設計即正確”。PCell 在版圖中生成,其參數從原理圖器件匯出;當用戶在 S-Edit 中點擊 Publish to SDL (發佈到 SDL) 時,PCell 按照在原理圖中的排列順序佈局。連接功能使版圖設計人員可以看到實例之間的圖形化飛線連接,這對佈線過程很有幫助。飛線可以按照 SDL Navigator 中的單個走線或多個走線來顯示,顏色可以由使用者通過功能表配置。

圖 12:L-Edit 版圖編輯器環境。

點擊原理圖中的設計實例可以高亮顯示版圖中的相應實例,反之亦然,這樣便可在 S-Edit (西門子的原理圖輸入和設計輸入工具) 與 L-Edit IC (西門子的物理版圖工具) 之間進行交叉顯示。

高級編輯功能

在諸如運算放大器之類的電路中,器件需要特定對稱結構的版圖。當使用電晶體、電阻器或電容器時,如果不使用特定的對稱結構版圖,就會出現相當多的匹配錯誤。對齊工具列、基點、物件捕捉、交換實例和複製功能使得佈局佈線更容易。

•基點就是用戶可以以特定點作為參考點進行編輯操作,支援使用遊標或特定座標進行參考點的設置。

•在繪圖、移動或編輯期間,利用物件捕捉工具列可以輕鬆捕捉物件。設計人員可以啟用不同的捕捉模式,如頂點、中點、邊緣、實例導線中心線、矩形中心點和管腳。

保護環生成器

Siemens L-Edit IC 可以自動生成多層繞線設計,以用於創建保護環。這種保護環常用在實例單元及所選模組周邊。預設保護環範本可以使用晶圓代工廠 PDK 中的標準過孔,使用者也可以自行配置。

圖 13:保護環生成器選單。

利用 Rule-Aware Layout 實現始終正確的版圖設計

L-Edit IC Rule-Aware Layout 會在使用者編輯版圖時顯示違規,從而説明用戶創建一次通過的緊湊且無錯誤版圖。此功能會檢查版圖中各圖層圖形間的違規,涵蓋層次化結構內各單元、圖形間的檢查。該工具可以在使用者編輯時顯示兩個邊緣之間的距離,顯示違規標記,以及利用 Rule-Aware Layout 防止違規——即不允許用戶繪製或編輯會導致違規的形狀 (可選功能)。

利用 Oasys 和 Nitro 完成數位實現

混合訊號設計方法

類比 / 混合訊號設計人員面臨著在混合訊號設計中實現越來越多數位內容的挑戰。本節說明這些設計的數位實現,以及使用者可以輕而易舉地集成各種混合訊號模組或 IP 元件。無論是設計具有少量數位控制的類比 IC,還是設計更複雜的混合訊號 ASIC,Siemens EDA 的 Tanner Digital Implementer (TDI) 軟體都有能夠滿足物理實現的理想解決方案。

圖 14:來源:Stargazer Systems, Inc.

利用 Oasys 和 Nitro 完成數位實現

TDI 可以支援混合訊號設計流程中的兩種不同模式的物理實現。

•“類比為頂層” (AOT),適用於以類比為中心的設計,數位控制邏輯單元被整合在原理圖設計當中

•“數位為頂層” (DoT),適用於以數位為中心的設計,類比 / 混合訊號 IP 通過網表驅動的 HDL (Verilog/VHDL) 流程導入

TDI 解決方案

TDI 提供易於使用的數位綜合和佈局佈線解決方案,其針對 22nm 及以上的模擬專有平面節點進行了優化。TDI 由 Oasys-RTL™ 軟體和 Nitro® 佈局佈線引擎驅動,每個許可證可以處理 75000 個實例,最多可以堆疊 4 個許可證。Oasys 已獲專利的 “PlaceFirst” 綜合技術通過在綜合之前執行佈局來改善 RTL 優化,高級別優化可以在 RTL 級別而反閘級別執行。Nitro 的高性能時序驅動的佈局佈線與已獲專利的多工藝角、多模式 (MCMM) 分析和優化架構一起,確保設計在時序、信號完整性、電源和麵積方面收斂。TDI 支援佈局規劃和電源規劃功能、時鐘樹綜合、用於 DFT 的掃描鏈插入以及低功耗設計方法。

TDI 已集成到基於 OpenAccess (OA) 開發的 Tanner 物理版圖工具 L-Edit IC 中;OA 是一個高級資料庫,為積體電路的設計提供全面的開放式標準資料模型和 API。

Oasys 和 Nitro 從 L-Edit 中的圖形介面驅動的嚮導啟動。該嚮導簡化了數位佈局佈線工具所需的複雜設置。數位設計的新手會發現圖形介面直觀易用,可快速上手,投入較少時間就能成為數位“大牛”,縮短周轉時間。經驗豐富的混合訊號設計人員可以從命令列運行 Oasys 和 Nitro。兩種使用模式均允許訪問參考流程腳本,以支援進一步定制。

Nitro 參考流程

TDI 運行 Nitro 參考流程,後者是一組統一的腳本,讓 IC 設計人員無需全面瞭解命令和選項就能運行 Nitro 佈局佈線。Nitro 參考流程如圖 15 所示。

圖 15:Nitro 參考流程。

利用 Calibre 進行物理驗證

Calibre Interactive 與 L-Edit IC 集成

設計人員需要能夠加快產品上市時間的工具。對類比 / 混合訊號 (AMS) IC 設計進行物理驗證時,速度是關鍵。Calibre 驗證工具套件與 Tanner L-Edit IC Layout 集成,從而能夠精確找出錯誤、快速完成修改並加快調試速度。所有主要晶圓代工廠都採用 Calibre 作為 sign-off 標準,這就保證了驗證結果的準確性,為流片一次性成功奠定了基礎。以下 Calibre 物理驗證和提取工具可以直接從 L-Edit 啟動:

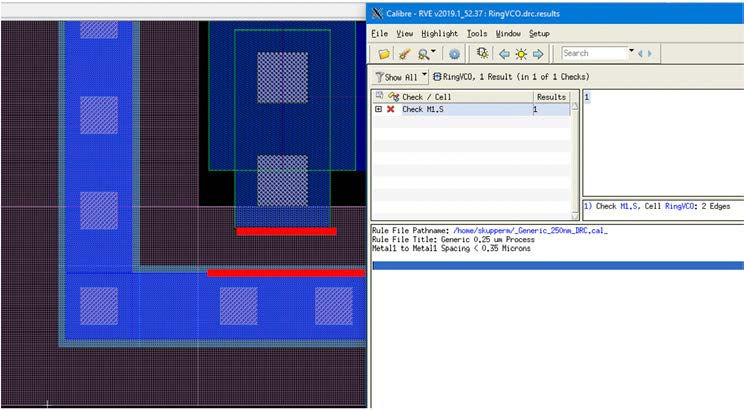

•Calibre nmDRC™ 確保物理版圖順利投產製造。使用晶圓代工廠的準確且經驗證的規則集快速調試違規情況,從而進行物理驗證 Signoff。

圖 16:DRC 結果。

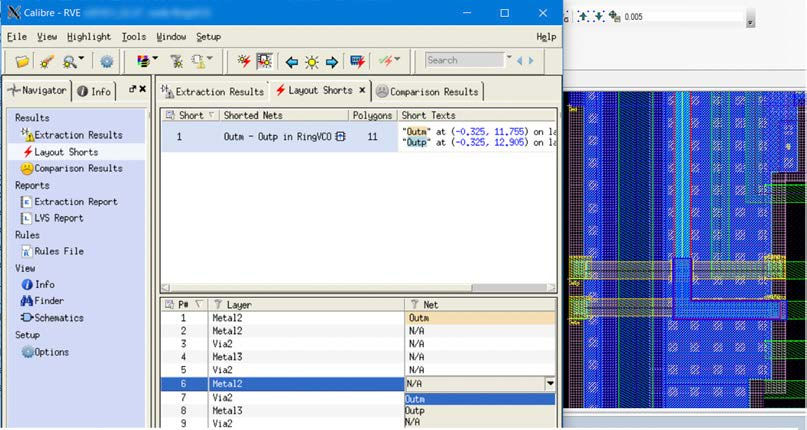

•Calibre nmLVS™ 檢查物理版圖和原理圖的電路連接 / 拓撲關係是否一致。Calibre nmLVS 提供器件幾何測量、可程式設計電氣規則檢查和精密的互動式調試功能,例如利用交互顯示突出顯示走線和器件,以確保電路驗證準確。

圖 17:LVS 短路定位器介面。

•Calibre xRC™ 幫助驗證版圖的寄生效應不會對設計的電氣性能產生不利影響。它還能為全面的版圖後模擬及分析提供準確的寄生資料。

•Calibre RVE™ 將解決方案整合在一起,提供圖形結果查看環境,然後通過肉眼快速識別設計問題以及交互選擇 L-Edit 和 S-Edit 中的相關問題,進而減少調試時間。

圖 18:Calibre 結果檢視器 (RVE)。

Calibre RealTime

Calibre RealTime 工具列支援定制和類比 / 混合訊號設計流程按需進行 Calibre sign-off 設計規則檢查,就設計規則違規提供即時回饋和合規建議,從而提高設計速度和結果品質。安裝 L-Edit 工具後,Calibre RealTime 工具列和選項自動可用。

Calibre RealTime 用戶端會載入完整的 Calibre 規則集,同時允許編輯方法,讓用戶能夠控制每次 Calibre 運行要執行哪些檢查。使用此集成方式運行 DRC 時,該工具僅對使用者可以在螢幕上看到的那些版圖區域運行 DRC。

結語

本文介紹了 Siemens EDA IC 全流程解決方案組合如何能説明設計人員設計、驗證和集成各種混合訊號模組或 IP 元件,其中每個模組或元件都包含層次化的緊密集成類比和數位電路,包括記憶體和 I/O 管腳。無論是設計具有少量數位模組的類比 IC,還是設計更複雜的混合訊號 ASIC,Siemens EDA 都有全流程解決方案來應對混合訊號工程師在進行 22nm 及以上的成熟 (平面) 製程節點設計時遇到的挑戰。

Comments