top of page

Search

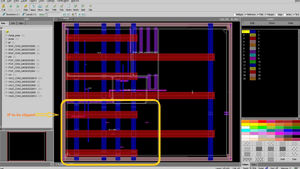

Save yourself the time—here’s a way for you to view native block instances from a full-chip context

By Ritu Walia Imagine this: You primarily work on the design of a sub-block of an application-specific layout design, or perhaps an intellectual property (IP) block for a system-on-chip (SoC). You’ve designed your block, and it’s ready for the SoC team. As you work hand-in-hand with the team striving to deliver the SoC within the (forever) limited time-to-market window, you face a multitude of challenges—complex design rule checking (DRC), iterative debugging, combined with t

Dec 12, 20231 min read

西門子與台積電合作 助客戶實現IC最佳化設計

西門子數位化工業軟體宣佈與台積電深化合作,展開一系列新技術認證與協作,多項西門子 EDA 產品成功獲得台積電的最新製程技術認證。 台積電設計基礎架構管理部門負責人 Dan Kochpatcharin 表示:「台積電與包括西門子在地的設計生態系統夥伴攜手合作,為客戶提供經過驗證的設計解決方案,充分發揮台積電先進製程技術的強大效能和功耗優勢,幫助客戶持續實現技術創新。」 Calibre 獲得台積電的 N2 製程認證 用於積體電路(IC)驗證 sign-off的 Calibre nmPlatform 工具已成功獲得台積電 N2 製程認證,可為早期採用台積電 N2 製程的廠商提供全面支援。獲得認證的 Calibre 工具包括 Calibre nmDRC 軟體、Calibre YieldEnhancer 軟體、Calibre PERC 軟體和 Calibre nmLVS 軟體。 台積電同時對用於電晶體層級電遷移(EM)與 IR 壓降(IR sign-off)的西門子 mPower 類比軟體進行 N4P 製程認證,雙方共同客戶現可以運用 mPower 獨有的

Oct 17, 20233 min read

Why take chances with your PV job setups when a winning alternative is available?

By Richard Yan Are you interested in optimizing your integrated circuit (IC) physical verification (PV) flows? How does automating the tedious manual setup of your PV jobs sound? With the option to save your configuration for future iterations? All this and more can be achieved with the user-friendly Calibre® Interactive graphic user interface (GUI), saving you time and effort in your iteration cycles, and boosting designer confidence! With the never-ceasing advance through I

Sep 5, 20232 min read

How can I run reliability checks early in the design cycle?

By Hossam Sarhan and Alexandre Arriordaz With the increasing complexity of design layouts and shorter tapeout cycles, waiting until signoff verification to find and correct errors is no longer practical for integrated circuit (IC) design teams. To achieve tapeouts on schedule, designers must now apply reliability verification checks throughout the design flow, from intellectual property (IP) level to full-chip level, to ensure they meet design schedules while confirming desig

Jun 6, 20232 min read

Cross-platform database validation: Don’t add applications without it!

By James Paris The OASIS* database format is a widely used industry standard in electronic design automation (EDA) software for integrated circuit (IC) design flows. While the OASIS standard provides a set of rules for the format and content of the file, different EDA tools may create different solutions to represent the same layout in OASIS format. These variations in the content and structure of the resulting databases may cause significant issues in the production IC desig

May 30, 20231 min read

Why take chances with your PV job setups when a winning alternative is available?

By Richard Yan Are you interested in optimizing your integrated circuit (IC) physical verification (PV) flows? How does automating the tedious manual setup of your PV jobs sound? With the option to save your configuration for future iterations? All this and more can be achieved with the user-friendly Calibre® Interactive graphic user interface (GUI), saving you time and effort in your iteration cycles, and boosting designer confidence! With the never-ceasing advance through I

May 23, 20232 min read

How Siemens EDA is using the TSMC 3Dblox standard to change 3DIC verification

By John Ferguson In recognition of the growing need for a more holistic approach to three-dimensional integrated circuit (3DIC) design, TSMC introduced their 3DFabric™ technologies in 2020 to incorporate system design, 3D stacking, and their advanced packaging technologies, such as TSMC-SoIC™, InFO, and CoWoS®. That was quickly followed by the formation of the TSMC Open Innovation Platform® (OIP) 3DFabric Alliance to accelerate 3DIC ecosystem innovation and readiness even fur

Apr 25, 20233 min read

The secret superpower of early design verification

By Kesmat Shahin How many times, as you traversed across design stages and ran countless iterations, have you wished that you had a superpower to let you accomplish 100 things at the same time? Oh, and maybe a magic wand, so you could find and fix just actionable errors without even debugging? Unfortunately, superpowers and magic wands are pretty hard to come by in integrated circuit (IC) design, but with Calibre nmLVS Recon early design layout vs. schematic (LVS) checking, S

Apr 18, 20232 min read

bottom of page