【解決方案】從翻譯工具進化為效能核心:第二代 Calibre V2LVS 重新定義 LVS 驗證

- Enlight Technology

- 2 days ago

- 7 min read

By Wael ElManhawy & Samar Abd El-Hady

您是否曾感受到設計節點持續微縮,以及系統單晶片 (SoC) 設計日益複雜所帶來的壓力?您並不孤單。在這個步調快速的半導體世界中,縮短驗證執行時間並提升簽核信心至關重要。而 Verilog-to-LVS 轉換正位於這精密流程的核心,負責銜接您的 RTL 設計意圖與電晶體級佈局驗證。

此關鍵步驟若有任何差錯,都可能導致代價高昂的延誤、令人挫折的重工,甚至產出品質欠佳的晶片。這正是為何我們很興奮能分享此領域的一項重大突破:第二代 Calibre Verilog-to-LVS (V2LVS)。

V2LVS 的功能為何?

Calibre V2LVS 是 Calibre IC 驗證流程中的關鍵組件。您可以將其想像成一位極其聰明的翻譯官。它負責接收您的結構化 Verilog 網表(Netlist)——這些網表以高階形式描述了您的設計結構——並將其轉換為 SPICE 網表。接著,SPICE 網表會被提供給如 Calibre nmLVS 等工具進行精確的佈局驗證(LVS)檢查,或是交由 Calibre PERC 進行可靠度驗證。

本質上,它確保了您在 Verilog 中設計的內容與您實際產出的實體佈局完全吻合(如圖 1 所示)。這對於晶片設計而言至關重要,對吧?

此流程通常從結構化 Verilog 網表開始,由 V2LVS 檢查其語法正確性。如果您有多個 Verilog 設計檔案,甚至是元件庫檔案,通常會先將它們合併成單一檔案,再輸入 V2LVS 處理。

此轉換步驟至關重要,因為它能建立下游驗證工具所需的詳細電晶體級描述,進而確保驗證工作得以徹底執行。

升級時刻:LVS 驗證的重大飛躍

原始的 V2LVS 工具多年來一直是自動化轉換的核心主力。然而,隨著設計團隊規模擴大與專案範疇增加,其單執行緒、單體式架構開始顯露疲態。想像一下,若試圖用僅有一條裝配線的工廠來運作大型複雜的生產,雖然可行,但很快就會陷入瓶頸!舊有的方法限制了擴充性與效率,尤其是在面對現今龐大的網表時。我們需要更強大、更高效且更具洞察力的解決方案,以追上日益嚴苛的設計週期、避免資源瓶頸,並縮短作業週轉時間。

第二代 V2LVS 不僅僅是一次更新,更是一場轉型!我們將 V2LVS 從基礎的翻譯公用程式,演進為一個強大且多功能的平台。我們的目標?是為您提供更快速、更直覺的除錯工具,增強 LVS 驗證流程的易用性與效能,並實現效能「左移」——在驗證週期早期提供更有效的結果,為後續流程節省時間並減少困擾。

揭秘核心:架構與效能的大幅提升

第二代 Calibre V2LVS 是一個重要的里程碑,它將一項關鍵的公用程式轉變為一個精密的平台。這第二代產品的核心變革在於全新的架構。第一代 V2LVS 是單體式架構,僅專注於 Verilog 對 SPICE 的轉換;而新設計則是模組化且具彈性的,允許 V2LVS 的不同部分獨立運作並分別進行優化。這不僅僅是為了提升速度,這種新配置也為未來的創新、更深層的設計洞察以及更簡易的除錯自動化開啟了大門。此外,它也為與 Calibre 生態系統進行更廣泛的整合奠定了基礎。

讓我們來看看這令人印象深刻的效能提升:

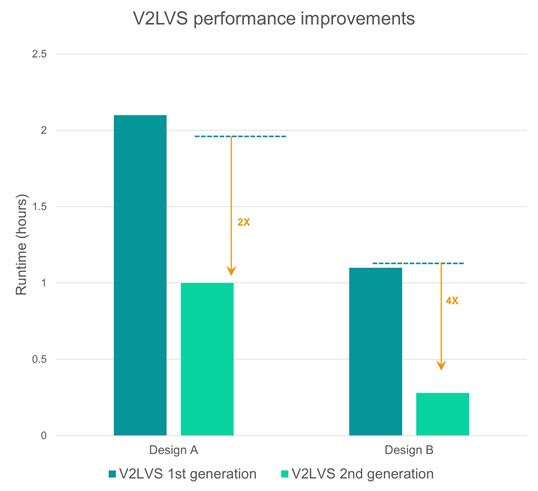

跨執行緒的平行模組執行:在先前的版本中,V2LVS 在單一 CPU 或執行緒上運作,依序執行所有模組。對於大型且複雜的網表來說,這是一個真正的瓶頸。新架構聰明得多:它允許不同的 V2LVS 模組在多個 CPU 上同時執行。這項創新展現了顯著的加速效果——在實際客戶的設計中,速度提升最高可達 4 倍!必須說明的是,這目前尚未達到完全的多執行緒(即同一個模組同時處理設計的不同部分),但這已是跨出的一大步,且為了追求更快的速度,完全多執行緒功能已在開發中。圖 2 顯示了新版 V2LVS 的效能提升。

大幅降低記憶體佔用:透過智慧架構與演算法的改進,V2LVS 現在使用的記憶體顯著減少——在某些測試情境中,降幅高達 92%!這是一項巨大的優勢。想像一下,您能夠處理以前因記憶體不足而無法執行的設計,或者在記憶體受限的環境或雲端平台上更高效地執行驗證流程。這項改進直接轉化為更好的擴充性與更低的營運成本。圖 3 顯示了 V2LVS 的記憶體改進情況。圖 3. V2LVS 記憶體佔用改善。

更優質的除錯功能與使用者體驗

另一個重點在於提升 V2LVS 的易用性,特別是在除錯方面。工程師經常在比對電路圖網表(Schematic Netlist)中主要與重複子電路之間的不一致時感到困擾。第二代 V2LVS 旨在透過一系列新功能來簡化此過程:

詳細的 V2LVS 日誌(Log):

實例轉換進度:對於極大規模的任務(例如超過 1,000 萬個實例),V2LVS 現在會提供轉換進度的即時更新。您再也不必盯著凍結的螢幕,懷疑程式是在運行還是已經當機!

模組統計數據:您可以獲得每個模組的詳細統計資料,包括模組名稱、所含埠(Port)數量、網線(Net)數量,以及帶有總腳位連接數的實例呼叫次數。這讓您能更清晰地掌握 V2LVS 內部的運作狀況以及資源分配。

累計摘要:每完成 10,000 個模組轉換,您就會收到一份累計摘要。這為長時間的執行過程提供了定期的檢查點與整體進度洞察,非常有幫助。

資源使用指標:系統現在會報告每個處理階段的記憶體佔用與執行時間,以及程式的總執行時間。這些數據對於分析流程、識別效能瓶頸以及優化未來執行的設定而言,具有極高的價值。

改良的重複項報告:兩項關鍵增強功能讓重複項的除錯不再令人頭痛:

您現在可以更精確地控制日誌中顯示的重複項警告數量,以便專注於最關鍵的問題,而不被海量資訊淹沒。

提供詳細的重複項報告,其中包含主要實例與重複實例的完整路徑,並精確標示出它們之間的不同之處。這能幫助您快速定位不一致的根源。

更聰明的電源/地線網線更名: V2LVS 會為具有多個文字標籤的網線建立更名檔案。以往電源或地線網線有可能被誤改名,雖然這看似微小的細節,卻可能導致下游流程出現嚴重的 LVS 或 ERC 問題。新版本確保電源與地線網線在更名過程中保留其原始設定的名稱,維持其在所有後續驗證步驟中的完整性。

對您的意義:實際效益

已經開始使用第二代 V2LVS 的客戶,正體驗到直接影響專案進度的顯著效益:

縮短 LVS 驗證的週轉時間: 這對於趕上緊迫的截止日期以及快速進行設計迭代(iteration)至關重要。

·大幅節省大型 SoC 設計的記憶體佔用: 讓驗證更複雜的設計成為可能,或是能在記憶體受限的環境(甚至雲端平台)中更高效地驗證現有設計。

提升轉換過程與不一致診斷的能見度: 不再需要憑空猜測!詳細的日誌與報告讓工程師能確切掌握狀況並快速解決問題。

增強對大規模設計的監控與除錯: 新功能提供了管理與排除最複雜驗證流程故障所需的工具。

這些優勢不僅加速了產品定案(tape-out)時程,更建立了對驗證結果的信心。這能協助團隊更有效地工作,並交付更高品質的晶片,而這正是我們追求的核心目標!

展望未來

第二代 Calibre V2LVS 是一項重大的進展,將這項關鍵的公用程式轉型為更先進的工具。憑藉著多模組平行處理、大幅減少記憶體佔用、擴充報告功能,以及朝向完全多執行緒發展的明確路徑,V2LVS 確實為 Verilog-to-LVS 轉換樹立了新的標竿。

隨著驗證工作的持續演進與新功能的推出,Calibre V2LVS 將維持其核心技術地位,確保現今最複雜的半導體設計能獲得精確且及時的電路驗證。這一切的目標都是為了讓工程師的工作更輕鬆,並讓您的設計更具韌性。

常見問題解答 (FAQ)

Q1:什麼是 Calibre V2LVS?為什麼它對半導體設計驗證至關重要?

A1: Calibre V2LVS (Verilog-to-LVS) 是 Calibre IC 驗證流程中不可或缺的一部分。它扮演著「極其聰明的翻譯官」的角色,將高階的結構化 Verilog 網表轉換為詳細的 SPICE 網表。這些 SPICE 網表隨後會被提供給如 Calibre nmLVS 等工具進行精確的佈局驗證 (LVS) 檢查,或交由 Calibre PERC 進行可靠度驗證。它之所以至關重要,是因為它能確保您最初在 Verilog 中的設計意圖與晶片的實體佈局精確吻合,進而防止代價高昂的錯誤與時程延誤。

Q2:第二代 Calibre V2LVS 有哪些關鍵進展與效能提升?

A2: 第二代 Calibre V2LVS 代表了一場重大的轉型。它採用了全新的模組化架構,允許不同的 V2LVS 模組在多個 CPU 上進行平行運算,在實際的客戶設計中,效能提升最高可達 4 倍。此外,它還大幅降低了記憶體佔用,在某些情境下可減少高達 92% 的記憶體使用量,讓您能夠在更大、更複雜的 SoC 設計上執行驗證。

Q3:新版 Calibre V2LVS 如何強化工程師的使用者體驗與除錯流程?

A3: 第二代 Calibre V2LVS 透過提供更詳細且具洞察力的日誌,顯著提升了使用者體驗與除錯效率。它能顯示即時的實例轉換進度、全面的模組統計數據、累計摘要,以及每個階段的資源使用指標(記憶體與執行時間)。它還提供了增強型重複項報告,讓使用者能更精確地控制警告訊息,並提供標示差異點的詳細報告;此外,更聰明的電源/地線網線更名功能可防止下游出現 LVS 與 ERC 問題。這些功能共同提升了能見度並加速問題的解決。

Comments