【解決方案】最佳化 ESD 防護:搭配 Calibre PERC 與 Solido Simulation Suite

- Enlight Technology

- Aug 11, 2025

- 4 min read

作者:Neel Natekar

對從事積體電路(IC)可靠度工作的工程師而言,最大的挑戰在於如何確保靜電放電(ESD)防護具備足夠強度的同時,又不對防護電路進行過度設計。過度設計不僅會增加晶片面積,還會降低高速與射頻(RF)電路的效能。對此,Siemens EDA 提出一項創新解決方案,結合 Calibre PERC 的可靠度驗證與 AI 加速的 Solido Simulation Suite,透過具備情境感知能力的 SPICE 模擬,協助工程師達到最佳化的 ESD 防護。本文將探討這個創新方法如何幫助工程師在防護與效能之間取得理想平衡。

了解挑戰:IC 設計中的 ESD 防護

ESD 對現代 IC 的可靠度構成重大威脅,特別是在設計特徵尺寸不斷縮小、整體設計複雜度日益升高的情況下。對於致力於達成嚴格 PPA(功耗、效能與面積)目標,同時又必須確保不犧牲可靠度的 IC 設計工程師而言,選擇合適的 ESD 設計策略至關重要。要做到這一點,工程師們必須清楚掌握可用的 ESD 設計邊界,同時避免對 ESD 防護電路出現設計不足或過度設計的情況。

傳統的 ESD 設計與驗證方法,在提供IC設計人員這些資訊時,是完全不足的。這些作法需要手動分割設計,或在 IP 或小區塊層級進行ESD模擬,再從較高層級的階層架構估算互連寄生效應,並將其拼接至元件模型,以建構分散式電源接地網路的模型。

傳統的ESD 驗證流程繁瑣,工程師為了保險起見,往往過度設計以避免潛在故障。這類作法不僅容易會讓使用者暴露在手動錯誤的風險中,也無法被信任用於signoff。

靜態 ESD 檢查的侷限

靜態 ESD 檢查是長期以來被採用的方式,透過晶圓廠所制定的點對點(P2P)電阻規則,來確保 ESD 防護結構的有效性。不過,這種方法在面對複雜設計,特別是處理涉及分散式 ESD 保護方案的複雜設計時,就顯得有所侷限。靜態檢查可能無法準確捕捉動態 ESD 防護電路的正確觸發,導致不必要的設計修改,甚至錯過潛在故障。

介紹具情境感知的 ESD 驗證

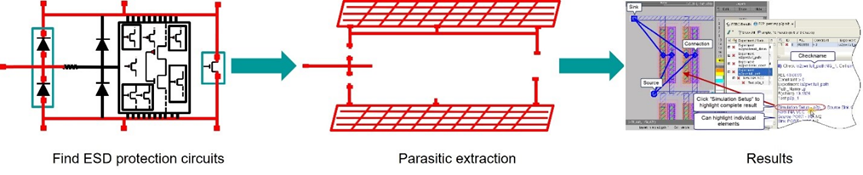

為了解決上述挑戰,Siemens EDA 推出具情境感知能力的 ESD 驗證流程,結合 Calibre PERC 與 Solido Simulation Suite 的優勢。這項創新解決方案利用 Calibre PERC 的智慧分析功能,僅識別和保留與 ESD 模擬相關的設計區塊,建立可模擬的netlist,再交由 Solido Simulation Suite 執行高擬真的 SPICE 模擬,準確捕捉ESD防護電路在真實操作條件下的行為。

這套強大的解決方案可讓設計人員在完全全自動化的流程中,執行全晶片的高擬真 ESD 驗證。透過 Calibre PERC 搭配 Solido,設計人員能準確掌握確切的設計邊界,同時清楚判斷哪些元件在何時、何處超出擊穿限制,而不無需進行任何手動修補或粗略估算。相較於傳統模擬技術,此解決方案在不犧牲準確度的前提下,能帶來高達 8 倍的效能提升。

使用情境一:驗證 ESD 放電路徑

這項技術的其中一個應用情境,是用來驗證在 ESD 事件發生時,若某些放電路徑未符合晶圓廠所訂定的電阻規範,是否會導致元件面臨擊穿風險。具備情境感知能力的驗證流程會自動找出不符合規範的放電路徑,並啟動模擬以判斷這些路徑是否對元件構成風險。工程師可根據模擬結果,決定是否向晶圓廠提出waivers,或進行不要的設計調整(如圖 2 所示)。

使用情境二:評估 ESD 設計餘裕

具備情境感知能力的 ESD流程的另一個強大應用是評估 ESD 防護電路的設計餘裕(design margins)。工程師可以指定想要觀察的頂層 IO 腳位,軟體便會自動模擬相關路徑。從模擬產出的詳細報告,可深入瞭解元件實際承受電壓與電流,有助於工程師更精確地判斷是否可針對晶片中特定區域進行 ESD 防護的微調或最佳化。

具備情境感知的 SPICE 模擬帶來的優勢

Siemens EDA 將 Calibre PERC 與 Solido Simulation Suite 整合,打造出一套顛覆傳統的 ESD 驗證流程,它包含多項優勢:

高擬真度分析:具備情境感知的 SPICE 流程可精確模擬 ESD 防護電路的動態行為,有效降低過度設計的風險,並確保防護效能達到最佳狀態。

全自動、零錯誤流程:全程自動化,無需人工介入,可降低人為錯誤風險,同時確保結果的一致性與可重現性。

提升生產效率:將模擬重點集中在最關鍵的電路路徑上,工程師可大幅縮短執行時間,進一步提升整體設計效率。

結語

隨著 IC 設計日益複雜且高度重視效能,傳統的 ESD 驗證方法已逐漸難以應付設計需求。Siemens EDA 所提供的具備情境感知能力的 SPICE 模擬流程,結合高精準度與高效率,為工程師提供一套強大的解決方案,協助在維持效能的同時,優化 ESD 防護設計。

Comments