top of page

客製化積體電路設計擷取

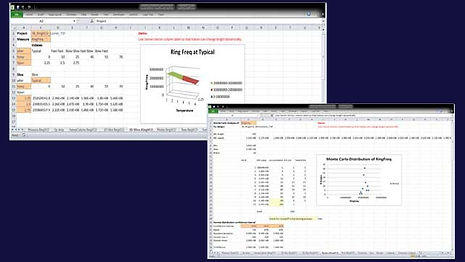

S-Edit 在處理最複雜的積體電路設計時,能有效提升生產力。完成電路圖建立後,即可設定並啟動所需的類比混合訊號模擬運算,並分析結果。之後可運用電路圖驅動佈局功能,引導佈局流程進行。

主要功能

處理您最複雜的全客製化設計

原生於 OpenAccess 單元支援多重視圖以實現類比混合訊號設計,包含:SPICE、原理圖、Verilog、Verilog-A、佈局、Verilog-AMS、VHDL 及 VHDL-AMS 視圖,透過 SDL 與 ECO 加速原理圖至佈局流程,支援超過 30 家晶圓廠的180餘種 PDK 採用 TCL/Tk 指令語言實現完全腳本化與擴充性。

功能完備的原理圖擷取環境

進階陣列與匯流排支援 支援繼承連接比較兩份原理圖並視覺化顯示差異在原理圖、佈局與 Calibre LVS報告間進行交叉探測,並標示網路/元件 可配置的原理圖電氣規則檢查(ERC)與版本控制工具整合 支援 Linux 與 Windows 雙平台。

模擬設定、啟動與結果檢視

快速檢視所有模擬執行的通過/失敗狀態將直流操作模擬結果與交流小信號元件參數直接反向註解至原理圖可為不同模擬分析組合或模擬器定義多個測試平台輕鬆設定掃描、邊界點、蒙地卡羅等分析流程追蹤並彙整專案中所有模擬測量數據。

Anchor 1

聯絡我們

bottom of page