top of page

Search

PCB design and analysis with PADS Professional Premium

Designing a printed circuit board can be a complex task if the application you are using does not provide the appropriate automation. Simplify the entire process by providing automation where it’s the most important. PADS Professional Premium delivers everything you need to design your simplest to most complex PCB designs. Full function, yet easy to use, with features and technologies like: Routing automation Can reduce PCB layout time by up to 80 percent. With electronics de

Jan 30, 20241 min read

Sanity check: Will automated fill back-annotation help?

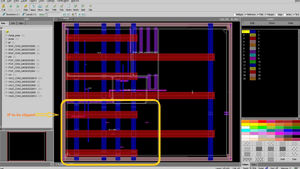

By James Paris Hey there, custom integrated circuit (IC) design engineers! If you’re knee-deep in the world of IC design, you know that dealing with fill flows is like walking a tightrope. On one hand, fill data is essential for ensuring your designs meet manufacturing density requirements. On the other hand, they can be a real headache when it comes to managing them effectively within your design environment. But wait, there’s good news! We’ve got a solution that’s going to

Jan 23, 20242 min read

PCB routing: art + automation

By Ray Macias and Gregory Beers PCB routing is one of the most enjoyable parts of PCB design , but also the most time consuming. It may take only a week to layout your board, but it could take you three months to route it unless you have the appropriate automation tools. PCB routing technology is more advanced than in years past, and yet, you can still be very creative and make a beautiful design. It makes sense to take advantage of the tools that are available to you when ro

Jan 16, 20244 min read

Streamlining semiconductor verification with the Calibre Interactive interface

By Slava Zhuchenya In the world of semiconductors, creating and verifying IC designs is no cakewalk. It’s a complex dance that involves a bunch of tools and simulations. Design companies rely on electronic design automation (EDA) tools to put IC designs through their paces before hitting the manufacturing line. These EDA tools are used to check if everything’s in order, from design rules to circuit layouts, ensuring that these intricate chips work as intended. Diving into the

Jan 9, 20243 min read

Navigating the maze of PCB routing: understanding interactive, auto, and sketch routing techniques

By Stephen Chavez In the world of PCB design, PCB routing plays a pivotal role in ensuring the efficiency and functionality of electronic circuits. Let’s explore the various PCB routing techniques, and shed some light on interactive routing, auto routing, and the empowering realm of sketch routing. Interactive routing: mouse-driven precision Interactive routing, the standard approach adopted by PCB designers across various PCB design tools, involves meticulous control over t

Jan 2, 20243 min read

Transistor-level EMIR analysis from custom design tools? It’s all about flexibility!

By Roger Kang How do you run transistor-level electromigration and voltage drop (EMIR) analysis—command line or an interactive invocation GUI? Does your layout designer have to wait for circuit designers to provide EMIR results and guidance before fixing any violations, and then iterate over and over until all EMIR violations are fixed? Maybe you’d prefer a new approach? How about one that lets layout designers deliver a high quality layout with no design rule checking (DRC),

Dec 26, 20232 min read

亞洲.矽谷物聯網產業大聯盟年會盛大舉行 龔明鑫:亞洲.矽谷將邁向3.0階段

龔明鑫:亞洲.矽谷方案未來將邁向3.0階段 展現台灣物聯網與5G實力 國發會主委龔明鑫致詞時表示,2016年在施振榮先生的號召之下,亞洲.矽谷物聯網產業⼤聯盟成立,現在看到數位轉型需求非常熱門,也算是超前部屬;而且聯盟會員持續成長,今年已來到435家,並且物聯網發展與應用也...

Dec 19, 20236 min read

Simplifying component research for efficient electronics design

By Matt Walsh Let’s delve into the challenges that electronic systems development organizations face and how an integrated part research solution, such as PartQuest Portal, can help streamline the design process, making it faster and more efficient. Challenges in electronics development Electronic systems development organizations are no strangers to complex challenges. Tight deadlines, resource limitations, the aspiration for first-pass success, and productivity hurdles coll

Dec 19, 20233 min read

Save yourself the time—here’s a way for you to view native block instances from a full-chip context

By Ritu Walia Imagine this: You primarily work on the design of a sub-block of an application-specific layout design, or perhaps an intellectual property (IP) block for a system-on-chip (SoC). You’ve designed your block, and it’s ready for the SoC team. As you work hand-in-hand with the team striving to deliver the SoC within the (forever) limited time-to-market window, you face a multitude of challenges—complex design rule checking (DRC), iterative debugging, combined with t

Dec 12, 20231 min read

bottom of page