top of page

Siemens announces certifications for TSMC’s latest processes

Siemens Digital Industries Software announced today at the TSMC 2023 North America Technology Symposium a range of new certifications and collaborations with longtime partner TSMC, resulting in key achievements toward enabling Siemens EDA technologies for the foundry’s latest process technologies. Calibre platform certified for N3E processes Siemens’ industry-leading Calibre® nmPlatform tool for integrated circuit (IC) verification sign-off is now fully certified for TSMC’s a

Apr 27, 20232 min read

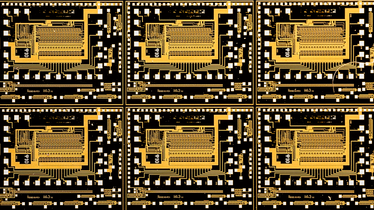

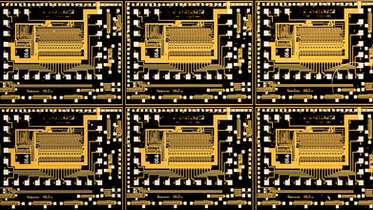

2022 L-Edit 進階實務 Workshop 圓滿成功

本周一(11/14)的 L-Edit 進階實務 Workshop 2022,為恩萊特科技的客戶進行 L-Edit 環境架構以及相關功能的介紹。 除了功能的操作之外,也透過實務案例針對 DRC Set Up、TDB Layout vs Layout Comparison、Docking Views、Wire Utilities 和 Mask Bias 等相關範例作介紹,加深學員們對 L-Edit 的了解,協助解決專案問題提升設計效率! 課程結束後,也獲得客戶們許多正面回饋 「今天講師講了很多小技巧,以及不知道的功能,對工作上提高非常多方便度」 「有初階的課程希望也有機會參加」 「非常完善!真是感謝!」 您也想參加 L-Edit Workshop 增加實務應用經驗值嗎? 歡迎與我們聯絡,了解更多詳情! 恩萊特科技股份有限公司 Enlight Technology Co., Ltd. www.enlight-tec.com 300052 新竹市東區關新路27號14樓之1 電話:03-602-7403 傳真:03-563-0016 sales@enlig

Nov 17, 20221 min read

Siemens partners with TSMC for 3nm product certifications and other technology milestones

Siemens Digital Industries Software today announced TSMC has certified a broad array of EDA solutions from Siemens Digital Industries Software for the foundry’s newest process technologies. In addition, recent collaboration between Siemens and TSMC has successfully established key milestones of relevance to mutual customers, including 3D IC enablement, further advancement of EDA in the cloud, and a range of other successful initiatives. “Siemens has been a long-standing ecos

Nov 1, 20223 min read

西門子、聯電強強聯手,加速 3D IC 開發時程

西門子數位化工業軟體今日宣布與聯電(UMC)合作,為聯電的晶圓對晶圓堆疊(wafer-on-wafer)及晶片對晶圓堆疊(chip-on-wafer)技術提供新的多晶片 3D IC 規劃、組裝驗證,以及寄生參數萃取(PEX)工作流程。 據悉,聯電開發出其全新混合鍵合(hybrid-bonding)3D 電路布局驗證(LVS)和寄生參數獲取工作流程,使用西門子 XPEDITION Substrate Integrator 軟體進行設計規劃與組裝,西門子 Calibre 3DSTACK 軟體進行晶片間的連接檢查,同時還使用 Calibre nmDRC 軟體、Calibre nmLVS 軟體及 Calibre xACT 軟體進行 IC 及晶片間延展實體及電路驗證任務。 而在雙方合作後,聯電也將向全球客戶提供此項新流程。藉由在單一封裝元件中提供晶片或小晶片(chiplet)彼此堆疊的技術,企業可以在相同或更小的晶片面積上實現多個元件的功能。與在 PCB 板上擺置多個晶片的傳統系統配置相比,這種方法不僅更加節省空間,而且能夠提供更出色的系統效能及功能以及更

Oct 4, 20222 min read

Improve your layout load time without capital investment?

By Roger Kang How many times has this happened to you—you waited for an hour to complete the loading of a layout file, only to have the job abort at 99% because the machine ran out of memory or disk space? Now you’ve wasted that hour, plus you have to find another machine with enough physical memory, or spend time cleaning up disk space, before rerunning your job. So much for your productivity that day. Even worse, that extra time might delay the tapeout schedule. As more con

Aug 23, 20222 min read

ASP Announces 2022 Best Support Websites

Al Hahn, Executive director of the Association of Support Professionals (ASP) today announced the winners of ASP's Best Support Websites 2022 competition. The top scoring websites were, in alphabetical order: NetApp Nutanix Red Hat Siemens Digital Industry Software In addition, SonicWall received a special award for Best Search. "Search is a common task for all support websites" noted Hahn. "For the past three years I have asked our judges if they could nominate any site for

Aug 16, 20221 min read

Parasitic extraction challenges and solutions for 5G IC design

What is 5G and what are its benefits? The fifth generation of mobile telecommunications technology, or 5G, is the next generation of wireless network technology, promising faster data speeds and more bandwidth than ever before. What does that mean for the average person? Think about cellphones, for one. People don't just use their phones for calling or texting anymore—they surf the web, check in with social media apps, watch movies, listen to music playlists, write blogs, tak

Aug 9, 202212 min read

西門子Calibre平台擴充EDA早期設計驗證解決方案

西門子數位化工業軟體近期為其積體電路(IC)實體驗證平台,Calibre擴充了一系列電子設計自動化(EDA)早期設計驗證功能,可將實體和電路驗證任務「shift left」,既在設計與驗證流程的早期階段就識別、分析並解決複雜的IC和晶片級系統(SoC)實體驗證問題,協助IC設計團隊及公司更快將晶片送交光罩製造(tapeout)。 在設計週期的早期識別並解決問題不僅有助於壓縮整個驗證週期,還能提供更多時間和機會來改善最終設計的品質。西門子使用合格的簽核(signoff)要求,為早期分析、驗證與最佳化策略提供經過調整的檢查支援,讓設計公司能簡化設計流程、提高設計師的生產力並縮短上市時間。 西門子EDA Calibre設計解決方案產品管理副總裁Michael Buehler-Garcia表示:「要在EDA領域保持技術領導地位,必須深入瞭解客戶在日常工作中面臨的特定挑戰,並在這些挑戰的驅動下持續進行改進。透過在Calibre中增添早期設計驗證功能,使我們的客戶無論處於哪一個設計階段,都可使用最新技術,將世界級的矽晶產品迅速推出市面。」 Calibre平台

Jul 28, 20223 min read

Siemens’ Calibre platform expands early design verification solutions

Siemens Digital Industries Software today announced a range of expanded electronic design automation (EDA) early design verification functionalities for its Calibre® platform for integrated circuit (IC) physical verification. Engineered to help IC design teams and companies get to tapeout faster, these new capabilities can help IC designers "shift left" their physical and circuit verification tasks by moving the identification, analysis, and resolution of complex IC and syste

Jul 19, 20223 min read

bottom of page