top of page

Fix first, finish faster!

By James Paris A few years ago, I came across some plans to build a simple bookshelf that would fit perfectly in my home. I already had...

Dec 6, 20212 min read

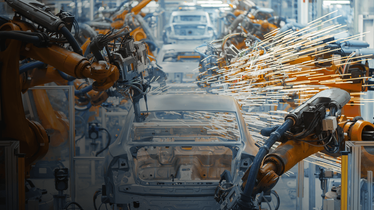

Enhancing Resiliency in Manufacturing through Connected Platforms, Increased Visibility, and Process

By: Deb Geiger, VP Global Marketing, Aegis Software Enhancing Resiliency in Manufacturing through Connected Platforms, Increased...

Nov 29, 20214 min read

In the EDA world, efficiency + ease of use = productivity (and profitability!)

By Shelly Stalnaker Electronic design automation (EDA) grew out of the need to make it easier and faster to design and manufacture integrated circuits. Nothing has changed since then, except…everything has changed. Just a couple of decades ago, we were entering “unknown territory”—the sub-nanometer era. Today, foundries and design companies are exploring 1nm process nodes. In all that time, the EDA industry constantly expanded functionality to address new design and manufactu

Nov 22, 20213 min read

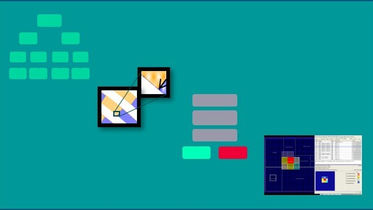

Improving Time-to-Market and Silicon Quality with a Streamlined IP QA Flow

By Wei-Lii Tan Recently Felipe Schneider (from the Solido Crosscheck applications engineering team) and I hosted a live webinar on how to improve time-to-market and silicon quality by utilizing a better IP QA flow. The webinar garnered quite a bit of interest, and we got several great questions from people who tuned in, so I thought I would follow-up here with some additional information. It’s no secret that readily-available, high quality design IP has not only shortened ove

Nov 15, 20212 min read

西門子與台積電深化合作 持續認證設計工具

西門子數位化工業軟體近日在台積電(2330) 2021開放創新平台 (Online Open Innovation Platform®,OIP) 生態系統論壇中宣布系列與台積電合作帶來一系列的新產品認證,雙方在雲端支援 IC 設計以及台積電的全系列 3D...

Nov 8, 20213 min read

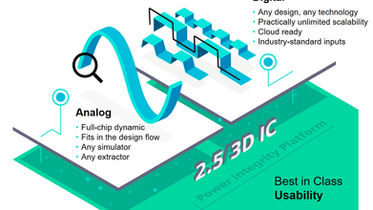

We know…power integrity analysis can be a really big pain, especially for really big designs

By Joe Davis Design teams use power integrity analysis to determine if the circuits in their designs will provide the intended...

Nov 4, 20213 min read

Is Your Organization a Leader or Laggard in Manufacturing Performance?

By: Deb Geiger, VP Global Marketing, Aegis Software How to gain a performance edge and become a "Best-in-Class" manufacturing leader....

Nov 1, 20215 min read

重新定義MES解決方案的概念

一個平臺交付工廠數位化 4.0和行業利益 獲得即時操作可視性和控制 一個IIoT平臺,在此平臺上,MES可以無縫地將人員、流程、系統和設備連接起來,從而通過自動化更快地做出更明智的決策。 提高生產力和效率 通過可配置的現代介面,甚至增強現實眼鏡,為操作員提供動態工作指令,從...

Oct 26, 20211 min read

Don’t like standing in lines? Get with the (right) programs!

By John Ferguson For a while, it appeared that the worst of the COVID pandemic was behind us. My mind immediately began focusing on a...

Oct 25, 20212 min read

bottom of page