top of page

Search

模態工程濾波器實現矽光子平台的高效波長分波

矽光子整合的關鍵挑戰 波長分波多工(Wavelength division multiplexing, WDM)技術能讓多個光訊號共用一條光路,是通訊與量子運算的核心技術。要將 WDM 整合到矽光子平台,須克服通道間干擾與損耗控制等問題,尤其在量子應用中,對於單光子訊號的完整性要求極高。 創新設計:抑制旁瓣的 Bragg 濾波器 傳統 Bragg 濾波器因結構對稱,易在反射光譜中產生旁瓣,影響濾波精度。研究團隊透過模態工程,設計出側牆對稱性漸變的濾波器,讓光模從基模逐漸轉換為高階模,再透過結構漸變控制模態互動,有效抑制反射旁瓣達 20 dB 以上。 模擬與製系統整合:模態加減耦合器實現高效選波 為擷取目標波長訊號,裝置結合一組針對模態特性設計的加減耦合器(modal add-drop, MAD),可精準導出選定波長,同時保有低插入損耗與高通帶純度。該裝置在矽絕緣體平台上製作並完成實測,驗證其低損耗與優異的旁瓣抑制能力。 結論 本研究提出的模態工程 Bragg 濾波器搭配 MAD 耦合器,可在矽光子晶片上實現精確、低損耗、多通道的波長分波功能。此技

Nov 3, 20251 min read

【白皮書】突破SERDES瓶頸:HyperLynx 如何用「一鍵」搞定百種高速介面規範?

高速設計的夢魘:手動SERDES分析的四大痛點 在PCB設計流程中,SERDES(序列化-解序列化)互連的通道分析始終是訊號完整性(SI)工程師的極大挑戰。您是否也深受以下困擾? 規格海茫茫: SERDES規範多達100多種,遠超DDRx規範的複雜度。每次遇到新的協定,都必須從零開始。 耗時且易錯的手動流程: 傳統上,您必須手動執行通道分解,並分別使用3D/2D場解算器進行建模,然後再將S參數模型重新連接。這個過程耗時且容易出錯。 高度仰賴EM專業: 為了確保模型的準確性,您必須具備深厚的電磁(EM)專業知識,例如準確地裁切互連區域,並確保回流路徑的完整性,這絕非易事。 合規性驗證壓力: 像是PCI Express Gen 4的規範可能長達上千頁,要在緊迫的設計時程內,完整理解並執行通道合規性驗證,幾乎是不可能的任務。 終結繁瑣!HyperLynx 帶來「智慧型、自動化」的分析新世代 HyperLynx SERDES分析 徹底顛覆了傳統手動流程。它將所有複雜的步驟自動化,內嵌了頂尖的EM與協定領域專業知識,為您帶來前所未有的效率與準確性: 1

Oct 29, 20252 min read

高效近紅外偏振控制:氮化矽晶片的光子整合關鍵技術

近紅外量子應用中的偏振挑戰 氮化矽(SiN)因具低損耗與寬頻透光特性,在可見光至中紅外應用中備受重視,尤其適用於量子光源如 InAsP 量子點(發光波段約 1 μm)。不過,若要實現精確的單光子操控,需具備高效偏振控制技術,而這在 SiN 平台上特別具挑戰性,因其對短波長偏振態的控制機制尚不成熟。 設計原理:PSR 結構中的旋轉與分離功能 本研究設計的偏振分離-旋轉器(polarization splitter-rotator, PSR)針對 910 至 980 奈米波段,具備兩階段結構:偏振旋轉與模式分離。 偏振旋轉(Rotation) 利用一段錐形波導將入射的 TM0 模式(橫向磁場)轉換為 TE1 模式(第一階橫向電場),透過移除上覆蓋層破壞對稱性,實現 TM-TE 模式混合與有效轉換。 模式分離(Splitting) 將旋轉後的 TE1 模式耦合至鄰近波導中的 TE0 模式,條件是兩波導寬度調整後,達到有效折射率匹配。原始 TE0 模式因不匹配則繼續前進至原輸出端。 模擬與製程驗證 採用有限差分與本徵模展開模擬工具(FDE、EME)進行波

Oct 27, 20252 min read

【白皮書】告別延宕與報廢!用Valor終結PCB新產品導入(NPI)的惡夢

您還在為PCB的「可製造性」煩惱嗎? 在競爭激烈的電子製造業中,將複雜的現代化印刷電路板(PCB)準時推向量產並上市,是PCB佈局工程師、新產品導入(NPI)工程師和製造商的共同挑戰。 然而,您是否經常面臨以下困境: 收到來自不同來源的設計資料,格式不一,難以整合? 設計中的可製造性問題,導致產品延宕發佈,甚至造成高成本報廢? 設計驗證流程依賴大量圖紙和輔助檔案,效率低落? 如果答案是肯定的,那麼您需要一種智慧化、整合式的解決方案,讓您從設計概念到量產的過程,都能一次到位。 【核心價值】從多個檔案到智慧整合式NPI模型 Valor NPI 帶來的變革,是從根本上統一了 NPI 流程。它將所有對於製造至關重要的資料,包含物料清單(BOM)、CAD資料,甚至表面處理、組裝生產板配置等資訊,全部整合進一個統一、全面且智慧的模型。 告別圖紙迷宮: 強化後的PCB產品模型包含所有製造定義,消除反覆驗證複雜傳統圖紙與文件的需求。 結構化資料優勢: 所有製造指示皆被整合為結構化資料,確保您的製造流程都基於相同的產品定義驅動,大幅提升效率與準確性。

Oct 22, 20252 min read

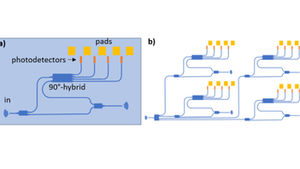

晶片化振動量測新突破:多光束頻率轉換器解決擴展瓶頸

雷射都卜勒測振技術的晶片化挑戰 雷射都卜勒振動儀(Laser Doppler vibrometry, LDV)是一種用於非破壞檢測與光聲感測的高靈敏度技術。過去依賴體積龐大的自由空間光學架構,但矽光子技術的導入讓 LDV 有望實現晶片化與大規模應用。不過,目前晶片式 LDV 最大瓶頸在於擴展性——每增加一個偵測點,就需增加對應的電子控制與讀取接腳,限制了應用規模。 本文提出一種創新的「多光束頻率轉換器」設計,有效解決上述問題,大幅減少電子連接數量,並實現多點同步振動量測的可能。 技術核心:多光束頻率轉換器運作原理 傳統 LDV 透過分光將光束拆分為參考光與測量光,並利用光混合與相位分析來量測目標震動。但若要同時監控多個位置,需併聯多組 LDV,導致接腳數線性增加。 本研究提出的多光束頻率轉換器,利用一組波導陣列與調變器模組,對單一入射光源施加具相位延遲的波形調變,產生不同的諧波(Harmonics)。這些不同調變的光訊號經由星狀耦合器(star coupler)後,依頻率分配到不同的輸出端,實現多頻率輸出功能。 模擬結果顯示,在理想調變條件下,不

Oct 20, 20252 min read

【白皮書】你的高速設計穩定嗎?揭密系統崩潰的隱形殺手:HyperLynx考量電源的模擬

您是否曾遇過明明訊號完整性(SI)模擬通過,但系統在實體運作時卻間歇性 (sporadically)發生故障或異常崩潰?尤其在高頻、高密度的設計中,例如DDR記憶體介面,這種情況幾乎成了設計工程師的夢魘。 問題的根源往往藏在一個容易被忽略的關鍵:電源傳輸網路(PDN, Power Delivery Network)。 大多數SI模擬器只採用理想化PDN模型,完全忽略了訊號與電源之間致命的交互作用。一旦硬體投產後才發現問題,輕則延遲上市、未達效能目標,重則整個產品線可能被迫取消。 揭露傳統模擬的「三大盲區」 現代PDN不僅要提供穩定的電源,更要為高速訊號提供一條乾淨的回流路徑。HyperLynx考量電源的模擬,正是為了解決這三個傳統工具無法精確捕捉的隱形殺手: 同時開關雜訊(SSN, Simultaneous Switching Noise):大量單端訊號(如 DDR 總線)同時切換時,會在驅動器電源軌上產生雜訊,對輸出驅動器進行調變,直接降低系統裕度。 導通孔間耦合(Via-to-via coupling):當訊號走線換層時,導通孔會將能

Oct 15, 20252 min read

III-V/SiN混合雷射產生Few-GHz光梳:無需外部驅動的整合方案

降 推動整合光頻梳走出實驗室 光梳(Optical Frequency Combs, OFCs)廣泛應用於分子光譜、LIDAR與光通訊系統,特別是密集波分多工(WDM)。目前OFC的晶片化整合已取得進展,但多數仍需外部雷射脈衝或電子驅動。為降低功耗與系統複雜度,研究者開始探索由整合式雷射自行產生的OFC。 本文探討一種基於III-V/SiN異質整合雷射的OFC生成機制,其重點在於透過四波混頻(FWM)、鬆弛振盪(Relaxation Oscillation)與非零線寬增益因子(Henry factor)所產生的非穩定單模態來激發多模頻率梳。 雷射結構:Vernier效應導入可控鏡面色散 該混合式雷射結構由InP系RSOA與SiN光子電路透過邊緣耦合方式整合。SiN波導上設有兩個耦合環形共振器,形成Vernier效應產生的等效反射率(reff),作為可調色散鏡面。雷射輸出從環形耦合器前段擷取,可透過相位調整區調控雷射頻率相對於reff的偏移位置。 模擬結果:Few-GHz間隔梳狀頻譜自發生成 使用時間域傳播波模型模擬RSOA內部的電場與載子分佈,並

Oct 13, 20252 min read

【白皮書】告別電源雜訊惡夢!HyperLynx PI 如何精準解決 PDN 設計的 DC 與 AC 挑戰?

隨著半導體設計朝向高頻、低電壓與高密度邁進,電源傳輸網路 (PDN) 已成為 PCB 設計中最常導致設計失敗或效能降級的關鍵環節。一個設計不良的 PDN,不僅會影響元件的供電穩定性,更可能產生難以追蹤的訊號完整性 (SI) 問題、過高的熱應力,甚至導致產品出現間歇性故障。 您是否厭倦了耗費大量的時間與資源,進行繁瑣的原型試製循環 (prototype spins),只為解決這些難以捉摸的電源問題? HyperLynx PI:從 DC 到 AC 的全面 PDN 掌控 HyperLynx PI 旨在解決這個複雜的挑戰,它提供一個整合式分析平台,讓硬體工程師和 PCB 設計人員能快速、精確地對 PDN 行為進行佈局前及佈局後的全面驗證,確保您的設計在電氣簽核前就已臻完美。 1.直流(DC)分析:告別壓降與熱點 在低頻率下,電阻損耗是影響供電穩定性的主因。HyperLynx PI 的 DC 分析能幫助您: △ 精確分析因電源層銅損所造成的壓降,識別供電不足的區域。 △ 標記出電流密度過高的區域,並透過PI/熱協同模擬預測溫度升高,避免板層或 IC 過

Oct 3, 20252 min read

【技術分享】使用諧波平衡法與 Quanscient Allsolve 在頻域中分析非線性系統

By Burcu Coskunsu 專家貢獻者 - Dr. Alexandre Halbach(技術長/共同創辦人)、Dr.-Ing. Abhishek Deshmukh(應用工程團隊主管) 重點摘要 非線性系統在真實應用中十分常見,而傳統的暫態分析方法往往又慢又容易產生雜...

Oct 1, 20258 min read

bottom of page