top of page

【解決方案】在IC設計中的前期驗證:加速且更智慧驗證的整體策略

By Michael White and David Abercrombie 隨著IC設計的複雜度持續上升,各家公司紛紛採用「前期驗證」這種前瞻性的策略,將關鍵的驗證任務提前至設計流程的初期,藉此加快產品上市速度並提升設計品質。這個概念最早由軟體工程師Larry Smith於2001年提出,當時用於軟體測試領域。「前期驗證」強調及早發現問題,並透過自動化工具提升生產力,同時降低在設計流程後期發生高成本錯誤的風險。在IC設計領域中,「前期驗證」已不僅是一種趨勢,而是一種轉型策略,能將驗證與優化提早納入設計周期中,讓工程師能更有效地應對日益增加的設計複雜度。 什麼是IC設計中的前期驗證? 簡單來說,前期驗證是指將關鍵的驗證與確認程序提前至設計流程的前段。傳統上,像是實體驗證與設計規則檢查(DRC)等關鍵驗證階段通常發生在設計流程的後期,這時若發現錯誤,可能會延誤量產並增加成本。透過將這些檢查「往前移動」——也就是所謂的「前期驗證」——設計人員能在正式簽核驗證前就提早發現並修正錯誤。 這種做法不只是小幅調整,而是面對IC設計(從系統單晶片 SoCs..

Jul 14, 20256 min read

【白皮書】Calibre® 進階對稱性檢查:提升類比與混合信號設計可靠性的關鍵利器

在處理類比或射頻設計時,您是否也曾因元件匹配不佳、對稱性錯位,導致效能不穩或反覆 tapeout 延誤?傳統佈局驗證方式無法捕捉具電氣與環境感知的對稱需求,導致除錯流程冗長。Siemens Calibre® 導入進階對稱性檢查技術,協助設計團隊在設計初期即發現並修正對稱性問題,顯著提升產品良率與驗證效率。 為什麼選擇 Calibre 對稱性檢查? 全面電氣感知:可辨識差分訊號、共心元件等對稱關係,結合網表與實體版圖進行交叉比對。 從前端到製造流程涵蓋:支援從佈局規劃、MP 染色、填充、封裝等階段的對稱檢查。 批次與互動支援:可在 Calibre RealTime 中即時視覺化錯誤,或批次檢查整體設計。 支援模糊對稱:提供面積、長度容差設定,協助工程師聚焦真正關鍵的 mismatch 問題。 無需額外開發:透過內建 XML 流程與圖樣比對技術,即可快速啟用檢查條件與除錯。 常見應用情境 驗證差分訊號路徑對稱性 確保多指元件匹配一致 排除不具設計風險的「容許差異」 辨識填充後產生的結構偏移 輔助記憶體、RF、光子設計穩健性分析 結論 Calibr

Jul 7, 20252 min read

【解決方案】在2.5D/3D積體電路中應對ESD挑戰:強固自動化驗證指南

By Dina Medhat 靜電放電(ESD)事件會對未加保護的積體電路(IC)造成嚴重損害。ESD事件是由兩個帶電物體之間突如其來且不可預期的電流流動所引發,可能的成因包括接觸、電氣短路或絕緣層擊穿。 無論其成因為何,所有ESD事件都可能導致金屬熔化、接面擊穿或氧化層失效。若未妥善預防,ESD可能在電子元件的任何製造階段或實際應用中造成損壞。ESD事件可能導致IC提早失效,或無法達到設計功能,這兩者都會對產品的市場聲譽造成不良影響。 當然,這些您早已知曉,因為您需依照設計規範手冊中所列的ESD設計規則,在電路圖與佈局中加入ESD防護機制(如圖1所示)。但現在您面臨的是2.5D或3D積體電路設計的ESD保護挑戰。該怎麼辦呢?您可以採用全新的Calibre 3DPERC(die2die)方法,進行自動化的ESD驗證,有效且精確地應對2.5D/3D IC設計中日益複雜的ESD韌性挑戰。 圖1:典型的ESD防護架構。 關於2.5D與3D積體電路 2.5D/3D積體電路已逐漸發展為解決各種設計與整合挑戰的創新方案。2.5D積體電路是將多顆晶粒並排放置於

Jul 2, 20253 min read

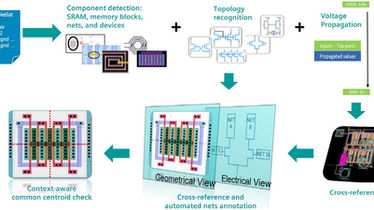

【技術分享】積體電路設計對稱性之進階驗證技術導論

By Jonathan Muirhead 積體電路(IC)設計,特別是在類比與射頻(RF)電路領域,需極為注重細節,以確保良好的可製造性與高效能的晶圓品質。在此過程中,「匹配」與「對稱性」的概念扮演關鍵角色,尤其是在差分對與電流鏡等拓撲結構中更是如此。接下來,讓我們簡要探討這些原則的演進,以及近期在驗證技術方面的進展,以確保設計符合相關規範。 為什麼對稱性很重要 對稱性不只是外觀上的美觀問題。在積體電路設計中,對稱性對於電路的功能與可靠性至關重要。差動對中繪製相同的 MOSFET 元件,必須在整個佈局流程中保持基本一致,才能維持相同的電氣性能。圖一說明了對稱性如何有助於降低應力與跨長度變異(ACVL)所帶來的影響。 圖一:用於元件參數匹配的一維共心(交錯式)技術。 傳統對稱設計技術 為了確保元件能圍繞中心軸保持對稱,常使用如「共心設計(common centroid)」等技術。這對於減少晶片製程變異所造成的匹配誤差至關重要。此設計方式會將元件配置於以某一中心點或中心軸為基準的對稱位置,使製程變異對雙方元件的影響一致,進而維持其匹配特性。 維持對稱

Jun 30, 20255 min read

【解決方案】透過 Calibre 互動式對稱性檢查進行前期驗證提升設計效率

By Sara Khalaf 對稱性在積體電路設計中扮演關鍵角色,有助於確保元件行為平衡、降低失配風險,並提升良率。然而,驗證對稱性傳統上是一項繁瑣且耗時的工作。許多設計人員常常需要花費大量時間手動檢查佈局,或撰寫複雜的驗證規則,卻仍可能在設計流程的後期,甚至是晶片製造後,才發現與對稱性相關的問題。 透過 Calibre 互動式對稱性檢查,設計人員現在可以在設計環境中即時掌握對稱性問題,這項強大的工具讓驗證任務得以前移至設計階段進行,更早發現並修正潛在問題,而非等到簽核階段或製造完成後才處理。這樣的方式可大幅減少設計迭代、降低返工成本,並加快送交製造的時程。此解決方案完全自動化、無需撰寫程式碼,只需幾下滑鼠點擊即可完成操作。 傳統對稱性檢查方法的挑戰 傳統的對稱性驗證方式存在多項限制,容易導致效率低落與設計時程延誤。以下是幾種常見技術及其缺點: 手動使用尺規測量: 設計人員需手動測量距離與元件位置以確認對稱性。這種方式不僅緩慢又繁瑣,也容易發生人為錯誤—若錯過關鍵測量,可能導致在設計流程後期才發現問題。 撰寫自訂規則: 有些設計人員會試圖撰寫自訂

Jun 25, 20253 min read

【白皮書】打破 DRC 瓶頸:為什麼你的設計流程該從「前期驗證」開始?

在現今 IC 設計節奏飛快的市場裡,時間就是競爭力。你可能也曾經歷過這樣的狀況:所有佈局都已就緒,卻在簽核階段才被 DRC(設計規則檢查)攔下,導致反覆修正、無止盡的執行等待,讓時程一延再延,甚至壓縮後段製程的驗證時間。 Siemens 最新技術白皮書指出:透過「Shift-left」設計思維,也就是將 DRC 驗證前移至設計初期,搭配 Calibre nmDRC Recon 的在地化區域檢查策略,就能有效解決這個老問題。 拒絕設計修正地獄,Calibre nmDRC Recon 帶來什麼? 在這份《The Power of Shift-left DRC Verification》白皮書中,Siemens 團隊分享了如何以 nmDRC Recon 為核心,打造更快、更輕量的驗證流程: 只針對「區域性檢查」執行,避免全佈局重跑、減少記憶體與 CPU 負擔 自動辨識「尚未完成」元件區域並套用 auto-waiver,避免誤報干擾修正焦點 搭配 Calibre nmLVS Recon SI 可快速排除短路、加速迭代收斂 結合split-deck平行執行

Jun 18, 20252 min read

【解決方案】透過雲端運算提升 Tapeout 後流程的可擴展性與效能

By Bassem Riad 隨著製程幾何尺寸持續縮小,計算光學對 CPU 資源的需求日益提高,不僅需要更強大的運算能力,還需要更多資源來支援日益複雜的演算法與更高精度的元件模型。執行如光學鄰近效應修正(OPC)、光罩製程修正(MPC)以及光罩資料準備(MDP)等 Tapeout 後流程(PTOF)任務,已經逼近傳統內部部署資源的極限,導致工作負載難以預測並面臨重大的擴展性挑戰。 Siemens EDA 為 AWS 所打造的參考環境,透過關鍵優化來因應這些挑戰,包括動態擴展以最大化資源使用率與執行效率,並透過硬體監控來微調運算實例的類型。Cloud Flight Plans 則引導使用者順利遷移至雲端環境,同時 Siemens EDA 也提供強大的叢集管理工具與大規模擴展能力。 雲端:解決長期以來難題的方案 雲端運算已被證實是解決 EDA 公司多年來運算挑戰的有效方案。以下是雲端運算在 Tapeout 後流程中之所以具備優勢(且日益成為必要選擇)的幾個原因: 成本效益: 省去前期資本投入,改採隨用隨付的計費模式,並可利用 AWS 的 Spot I

Jun 4, 20256 min read

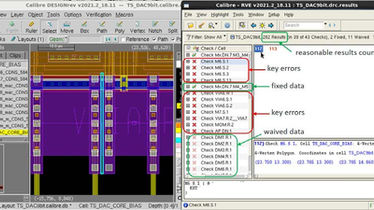

【白皮書】Calibre ® RVE 批次篩選:一種更快、更有效率篩選大型 DRC 結果資料庫的方法

在進行設計規則檢查(DRC)除錯時,您是否也曾為了開啟幾百 GB 的 RDB(結果資料庫)檔案、處理數百萬條錯誤訊息而感到頭痛?傳統的 GUI 篩選方式,不僅耗時,也佔用大量記憶體資源,導致整體效率低落。Siemens 推出的 Calibre® RVE 批次篩選流程,提供了一種更聰明、更快速的除錯選擇,讓設計團隊能夠專注處理最關鍵的問題,大幅提升 tapeout 效率。 為什麼選擇 Calibre RVE 批次篩選? 避免完整載入超大 RDB:批次篩選流程可在不載入整個 RDB 的情況下,根據篩選條件產出較小的 RDB 檔案。 記憶體資源大幅下降:例如,從一個 110GB RDB 中萃取部分檢查結果的過程中,記憶體使用量從 77.7GB 降到 1.5~10.5GB。 執行效率明顯提升:相比 GUI 篩選需 1 小時,批次篩選與載入所需總時間不到 1 小時,還能一次產出多組針對性資料。 彈性建構篩選條件:支援檢查名稱、屬性範圍(如 CD 值)等邏輯組合,建立高度客製的篩選條件。 跨團隊重複使用:篩選語法可簡易分享與重用,強化團隊協作效率。 常見應用

Jun 2, 20252 min read

【成功案例】解決 IR 壓降與佈局瓶頸:Calibre DesignEnhancer 如何簡化積體電路設計流程

By Jeff Wilson 身為一位積體電路設計工程師,你知道要達成最佳佈局不只是通過設計規則檢查(DRC)這麼簡單——更重要的是在電性效能、製造可行性與上市時程壓力之間取得平衡。一個經過良好優化的設計不僅能減少昂貴的反覆修正週期,還能確保更佳的效能並加快產品上市速度。然而,即使有先進的設計工具,要在符合嚴格的 DRC 標準的同時,還要針對電遷移與 IR 壓降(EMIR)進行優化,仍然是一項重大挑戰。 IC 設計師需要能簡化設計流程,同時維持良率與電源完整性的工具。隨著半導體佈局愈加複雜,如何同時確保 DRC 合規與電性效能,變得愈發困難。Calibre DesignEnhancer(DE)提供一套以自動化為核心的解決方案,協助設計師有效率地優化佈局。現在,就讓我們來探討 IC 設計師面臨的主要挑戰,以及智慧自動化如何強化整體設計流程。 IC 設計的瓶頸:那些拖慢設計流程的挑戰 Place-and-route(P&R)工具在插入電路元件與進行連線方面表現不錯。然而,由於 P&R 解決方案無法全面理解所有設計規則,為了確保設計能通過 DRC..

May 21, 20255 min read

bottom of page